设计根据锁相环的基本原理,基于ADI公司频率合成芯片ADF4351,通过单片机ADuC7023程序控制,设计与实现一种高性能可调频率源,并且测试输出频率在935MHz,相位噪声-84.76dBc@1kHz,-91.30dBc@10kHz,杂散信号较低,测试结果表明该频率合成器输出信号稳定,噪声系数较低。

设计根据锁相环的基本原理,基于ADI公司频率合成芯片ADF4351,通过单片机ADuC7023程序控制,设计与实现一种高性能可调频率源,并且测试输出频率在935MHz,相位噪声-84.76dBc@1kHz,-91.30dBc@10kHz,杂散信号较低,测试结果表明该频率合成器输出信号稳定,噪声系数较低。

关键词:频率合成器;锁相环;相位噪声

中图分类号:TN742

随着通信技术的不断发展,系统对频率源所提供频率稳定度、输出频率范围、信号幅度等指标要求越来越高,而直接制造高精度、高稳定度和低相位噪声一系列晶振也不现实,因此采用频率合成技术,通过对参考频率进行加、减、乘、除运算,就可以由一个标准频率源产生一系列具有高稳定度和准确度的频率信号。所以频率合成技术目前得到了广泛的应用,是现在通信系统里边不可缺少的一个重要模块。[1-2]

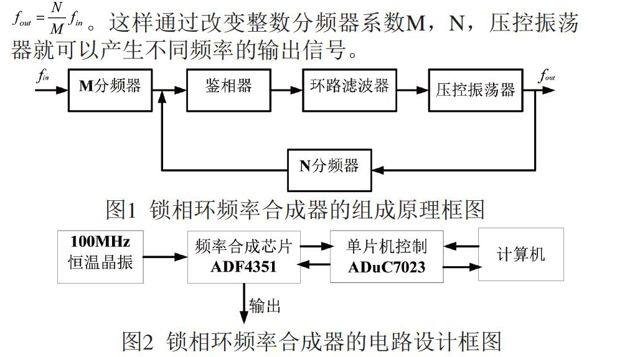

基于锁相环频率合成技术,由于锁相环路相当于窄带跟踪滤波器,能很好地选择所需频率的信号,抑制杂散分量,避免了大量使用滤波器,而标准频率源具有高的长期频率稳定度,锁相式频率合成器把这二者结合在一起,使其合成信号的长期稳定度和短期稳定度都很高[3]。锁相环频率合成器的组成原理框图如图1所示,在压控振荡器与鉴相器之间的锁相环反馈回路上增加整数分频器,就形成了一个可调频率合成器。输入信号fin经过M分频器后进入鉴相器,鉴相器把N分频器反馈信号与M分频器信号比较,产生一个反应两者大小的电压信号,过低通滤波器得到压控电压,当环路处于锁定状态时,输出信号频率: 。这样通过改变整数分频器系数M,N,压控振荡器就可以产生不同频率的输出信号。

本设计采用高品质恒温晶振100MHz作为参考频率,基于ADI公司频率合成芯片ADF4351,通过单片机ADuC7023程序控制,设计与实现输出频率35MHz~4400MHz,输出功率可调、低杂散和低相位噪声的可调频率源。

1 频率合成器电路设计

本设计的整体设计框图如图2所示,系统控制部分由单片机ADuC7023,频率合成芯片ADF4351、恒温晶振和计算机组成。系统采用外部100 MHz恒温晶振作为参考频率,同时采用ADuC7023作为控制芯片来配置锁相环芯片ADF4351内部的分频器和控制器,完成锁相环芯片的外部输入以及配置。通过计算机来控制锁相环芯片输出不同的频率:由计算机串口将数据传递给单片机ADuC7023,对锁相环芯片相应寄存器重新配置,得到不同的输出频率。

1.1 ADF4351芯片介绍与寄存器配置

锁相环芯片ADF4351具有一个集成电压控制振荡器(VCO),其基波输出频率范围为2200 MHz至4400 MHz。此外,利用1/2/4/8/16/32/64分频电路,用户可以产生低至35 MHz的RF输出频率。通过编程,可以调整内部分频器数值和输出功率高低,而且锁相环芯片还有一个锁定检测引出管脚LD,通过对此端口的配置可以检测锁相环芯片的内部工作状态。对芯片配置完成之后,重新加电可使频率合成器正常工作。

根据锁相环配置要求,结合ADF4351数据手册,设置输出频率RFout为935MHz,输出功率5dBm,fPFD=20MHz,fREF=100MHz,得到寄存器参数:R0=005D8000;R0=08008009;R0=00014F42;R0=000004B3;R0=00AA00FC;R0=00580005。

1.2 环路滤波器设计

环路滤波器实质是一个低通滤波器,由电阻、电容可能还有放大器组成。它的输入是电荷泵输出,滤除高频成分和噪声,取出其平均作为输出来控制VCO[4]。随着应用对PLL性能要求的提高,引入了环路滤波器来改善VCO控制电压的频谱纯度,提高系统稳定性。无源二阶环路滤波器是应用中最简单的环路

滤波器,由于其电阻值非常小,有效降低滤波器热噪声减小环路相位噪声,同时可使与VCO相连接电容值最大,从而减小VCO输入电容的影响。根据ADI公司提供的锁相环电路配套设计软件ADIsimPLL,设置输出频率在935MHz,环路带宽50kHz,相位裕度45°,具体参数如图3所示,C1、C2、C3、R1、R2只是理论参考值,具体测试需要对数值进行调试、优化。

1.3 硬件电路设计

图4为ADF4351外围部分电路图,包括芯片的关键参数、输出匹配参数以及环路滤波器设计。通过CLK、DATA、LE端口对ADF4351寄存器进行配置,如果输出频率锁定,则通过端口LD回传给控制芯片ADuC7023。

2 硬件电路实现与测试结果

本设计采用四层电路板,供电电压5 V,100 MHz恒温晶振作为参考频率,焊接调试完成电路如图5所示,板子尺寸6cm×5cm。

设置频率合成器输出频率为935 MHz,输出测试结果如图6所示,相位噪声-84.76dBc@1kHz,-91.30dBc@10kHz,杂散信号较低,测试结果表明该频率合成器输出的频率信号稳定,噪声系数低。

3 结束语

本设计基于频率合成芯片ADF4351,得到一个频率可调的高稳定、低噪声的频率源。以输出频率935MHz为例,给出了频率合成器和环路滤波器设计中的关键参数。通过对硬件电路的调试和性能优化,实现了一个结构简单的频率源,解决了传统频率源带宽不够宽、频率源利用效率不高的问题。由于该芯片良好性能,使得设计出的电路具有体积小、功耗低的特点,因此,可能应用于测试设备、无线通信以及深空探测等领域。

参考文献:

[1]马国胜,杨鹭怡ADF4350低相噪频率合成器在射频无线通信设备中的应用[J].应用天地,2009(04):65-69.

[2]林巧莉.基于ADF4360系列的小型化频率合成器设计[J].电讯技术,2008(10):85-86.

[3]王家礼,孙璐.频率合成技术[M].西安:西安电子科技大学出版社,2009.

[4]胡志慧,姜永华,陈晓晨等.基于DDS+PLL的X波段频率合成器设计[J].国外电子测量技术,2008(07):39-41.

作者简介:张文轩(1995.11-),男,内蒙古人,本科在读,电子信息工程专业。

作者单位:北方工业大学 电子信息工程学院,北京 100144

扩展阅读文章

推荐阅读文章

推荐内容

77范文网 https://www.hanjia777.com

Copyright © 2015-2025 . 77范文网 版权所有

Powered by 77范文网 © All Rights Reserved. 备案号:粤ICP备15071480号-27